# Linear synchronization and circuit implementation of chaotic system with complete amplitude control\*

Chun-Biao Li(李春彪)<sup>1,2,†</sup>, Wesley Joo-Chen Thio<sup>3</sup>, Julien Clinton Sprott<sup>4</sup>, Ruo-Xun Zhang(张若洵)<sup>5</sup>, and Tian-Ai Lu(陆天爱)<sup>1,2</sup>

<sup>1</sup> Jiangsu Key Laboratory of Meteorological Observation and Information Processing, Nanjing University of Information Science & Technology, Nanjing 210044, China

<sup>2</sup> School of Electronic & Information Engineering, Nanjing University of Information Science & Technology, Nanjing 210044, China <sup>3</sup> Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210, USA

<sup>4</sup> Department of Physics, University of Wisconsin–Madison, Madison, WI 53706, USA <sup>5</sup> College of Teacher Education, Xingtai University, Xingtai 054001, China

(Received 11 July 2017; revised manuscript received 22 August 2017; published online 20 October 2017)

Although chaotic signals are considered to have great potential applications in radar and communication engineering, their broadband spectrum makes it difficult to design an applicable amplifier or an attenuator for amplitude conditioning. Moreover, the transformation between a unipolar signal and a bipolar signal is often required. In this paper, a more intelligent hardware implementation based on field programmable analog array (FPAA) is constructed for chaotic systems with complete amplitude control. Firstly, two chaotic systems with complete amplitude control are introduced, one of which has the property of offset boosting with total amplitude control, while the other has offset boosting and a parameter for partial control. Both cases can achieve complete amplitude control including amplitude rescaling and offset boosting. Secondly, linear synchronization is established based on the special structure of chaotic system. Finally, experimental circuits are constructed on an FPAA where the predicted amplitude control is realized through only two independent configurable analog module (CAM) gain values.

Keywords: complete amplitude control, amplitude rescaling, offset boosting, linear synchronization

**PACS:** 05.45.–a, 05.45.Ac, 05.45.Xt

## 1. Introduction

Chaotic signals have great potential applications in radar and communication engineering because of their broadband frequency spectrum.<sup>[1–20]</sup> However, this introduces a corresponding challenge to signal-conditioning since it is difficult to construct an amplifier or a polarity conversion circuit with a broadband frequency response. The chaotic signal usually cannot meet the amplitude requirement for practical applications. Polarity conversion is also critical since some integrated circuits require either unipolar or bipolar signals. Although some effort has been made to realize amplitude control for chaotic signal through total amplitude scaling and partial amplitude scaling, <sup>[21–24]</sup> the polarity control of chaotic signal has not received the same attention despite being essential in electronic engineering. <sup>[25–28]</sup>

Offset boosting is associated with the DC component of the variable, and our study shows that one or more variables in a chaotic system can obtain offset boosting by introducing a new constant. <sup>[26]</sup> Consequently the conversion between a unipolar chaotic signal and a bipolar signal can be realized

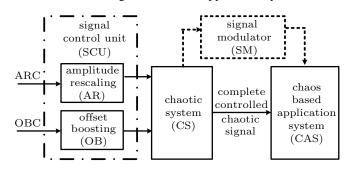

by a single DC source or a control rheostat rather than a complicated hardware peripheral unit. Foregoing research has allowed us to realize a system with complete amplitude control by using amplitude scaling and offset boosting. As shown in Fig. 1, the signal modulator is replaced by two controllers for amplitude rescaling and offset boosting, giving complete control of the chaotic signals for chaos application systems.

**DOI:** 10.1088/1674-1056/26/12/120501

Fig. 1. Application system with chaos.

In this paper, a whole linear control of chaotic signals is explored through amplitude and offset control in a single system, and a linear synchronization between two systems is described. We consider two cases of complete amplitude control

<sup>\*</sup>Project supported by the Startup Foundation for Introducing Talent of Nanjing University of Information Science & Technology, China (Grant No. 2016205), the Natural Science Foundation of the Jiangsu Higher Education Institutions of Jiangsu Province, China (Grant No. 16KJB120004), the Priority Academic Program Development of Jiangsu Higher Education Institutions, and the Natural Science Foundation of Hebei Province, China (Grant No. A2015108010).

<sup>&</sup>lt;sup>†</sup>Corresponding author. E-mail: goontry@126.com; chunbiaolee@nuist.edu.cn

where offset boosting can be accompanied by total amplitude control or partial amplitude control. In Section 2, we give two examples to show complete amplitude control through a dynamical analysis. In Section 3, the linear synchronization of these types of chaotic systems is studied. In Section 4, we design the corresponding circuits giving corresponding attractors, where they can be amplified or shifted with two separate single control units. The conclusion is given in the last section.

# 2. Offset boosting with amplitude control

### 2.1. Offset boosting with total amplitude control

In this type of chaotic system, offset boosting can be used to realize the transition between a unipolar signal and a bipolar signal. This is done by adding a constant, while total amplitude control can be used to realize a whole signal rescaling through a single coefficient. A few variable-boostable chaotic systems [34] meet this condition, such as chaotic systems Sprott J, Sprott P<sup>[35]</sup> and JD0,<sup>[36]</sup> where the nonlinearity resides in a single quadratic term, giving a coefficient for amplitude rescaling. Take Sprott J for example,

$$\begin{cases} \dot{x} = az, \\ \dot{y} = -by + z, \\ \dot{z} = -x + y + my^2 + c. \end{cases}$$

(1)

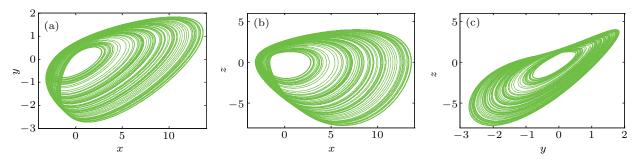

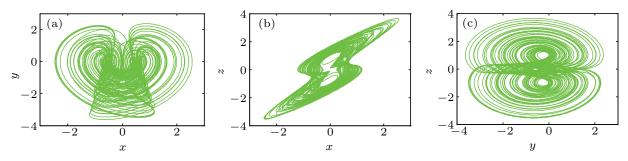

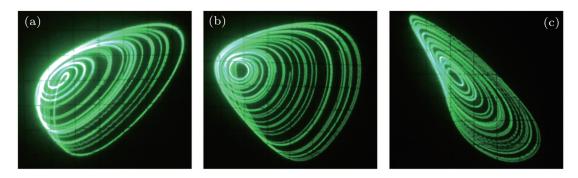

When a = b = 2, m = 1, and c = 0, system (1) is chaotic with Lyapunov exponents (0.0787, 0, -2.0787) and a Kaplan–Yorke dimension of  $D_{\rm KY} = 2.0379$ . The phase trajectory is shown in Fig. 2.

Fig. 2. (color online) Strange attractor of system (1) with a = b = 2, m = 1, and c = 0 and initial conditions  $(x_0, y_0, z_0) = (-1, 0.3, 0)$  in (a) x-y plane, (b) x-z plane, and (c) y-z plane.

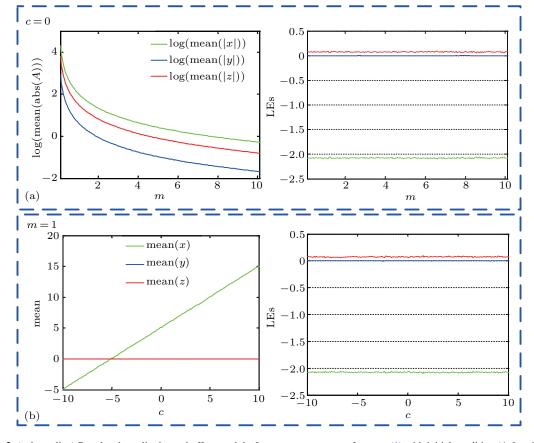

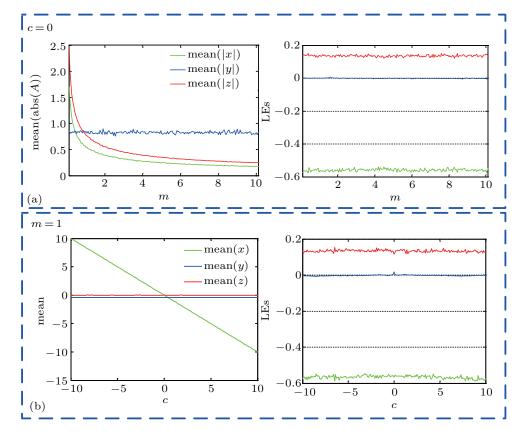

Fig. 3. (color online) Regulated amplitudes and offsets and the Lyapunov exponents of system (1) with initial condition (4, 0, -1/5): (a) amplitude rescaling with constant Lyapunov exponents and (b) offset regulating with constant Lyapunov exponents.

Here the parameter m is a total amplitude controller while the parameter c is an offset boosting controller. To show this, let c=0 and x=u/m, y=v/m, z=w/m to obtain new equations in the variables u, v, w, which are identical to system (1) with m=1; while fixing the parameter m and letting x=u+c, y=v, and z=w to obtain new equations with variables u, v, w, which are identical to system (1) where c=0. Therefore, the coefficient m controls the amplitude of all variables according to 1/m while the constant c controls the offset level of the variable x. Therefore, chaotic signal x in system (1) can obtain complete amplitude control through the coefficient m and the constant c.

As shown in Fig. 3, when a = b = 2, the amplitude of the signal x is inversely proportional to the parameter m, and the offset can be regulated to be proportional to controller c without changing the Lyapunov exponents.

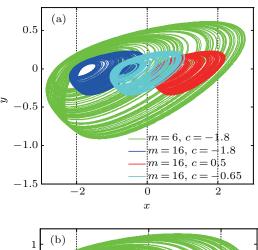

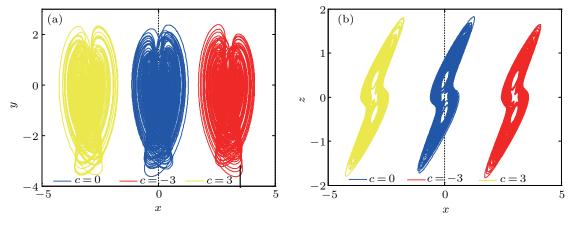

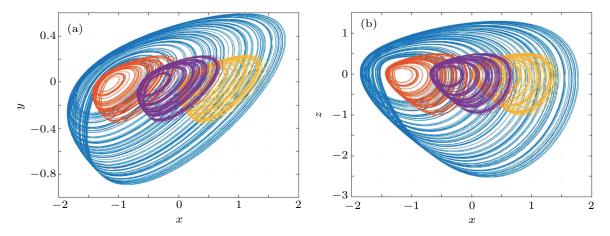

The relationship between offset control and amplitude rescaling can be used to transform a bipolar signal to a unipolar signal by adjusting the depth of offset boosting according to the signal amplitude. In order to increase the amplitude through the amplitude parameter, a larger boosting controller is required correspondingly. Once the boosting controller is introduced into the system, the amplitude controller will consequently modify the depth of boosting. Specifically, in Eq. (1), variable substitutions x = (u - c)/m, y = v/m, and z = w/mresult in new equations with variables u, v, w, which are identical to Eq. (1) with c = 0 and m = 1. Therefore, the amplitude controller m modifies the depth of variable boosting according to c/m (as shown in Fig. 4), while the absolute distance between two attractors caused by the offset controller becomes independent of the amplitude parameter. The interaction between the amplitude controller and the offset controller allows signal x to be positive, negative, or have both polarities on any desired scale. This can be identified in Fig. 4 by the attractors located on the negative half x axis (blue), positive half x axis (red) or in the whole x axis (cyan and green with different amplitudes).

**Fig. 4.** (color online) Chaotic attractors with different amplitude rescaling and offset controlling with initial conditions (x, y, z) = (1, 0, -0.2): (a) in x–y and (b) x–z plane.

#### 2.2. Offset boosting with partial amplitude control

New variable-boostable cases with partial amplitude control were found by an exhaustive computer search. [29] One of these cases has global attraction leading to a simple implementation since the initial conditions do not need to be revised accordingly,

$$\begin{cases} \dot{x} = ayz, \\ \dot{y} = 1 - mz^2, \\ \dot{z} = x + yz + c. \end{cases}$$

(2)

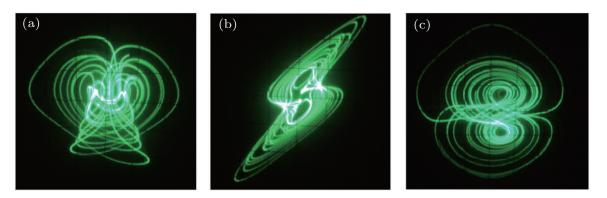

When a = 1, m = 1, and c = 0, system (2) is chaotic with Lyapunov exponents (0.1271, 0, -0.5526) and a Kaplan–Yorke dimension of  $D_{\rm KY} = 2.2299$ . The phase trajectory in different planes is shown in Fig. 5.

Fig. 5. (color online) Strange attractor of system (2) with a = 1, m = 1, and c = 0 and initial conditions  $(x_0, y_0, z_0) = (1, 1, -1)$  in (a) x-y plane, (b) x-z plane, and (c) y-z plane.

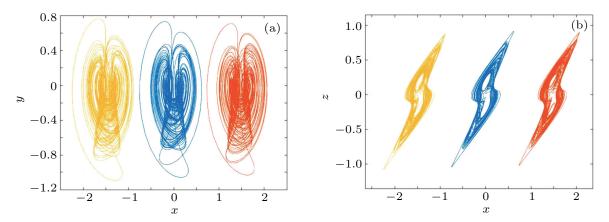

Here the parameter m is a partial amplitude controller while the parameter c is an offset boosting controller. To show this, we take c=0 and  $x=u/\sqrt{m}$ , y=v,  $z=w/\sqrt{m}$  to obtain new equations in variables u, v, w, which are identical to system (2) with m=1. Therefore, coefficient m controls the amplitude of variables x and z according to  $1/\sqrt{m}$  while leaving the amplitude of y unchanged. The variable x is boosted along the x-axis according to the constant c. Negative c boosts the variable in the positive direction, while positive c draws the variable backward in the negative direction. To show this, we fix the parameter m and let x=u-c, y=v, z=w to obtain new equations in the variables u, v, w, which

are identical to system (2) with c=0. A pre-fixed boosting controller will be modified by the amplitude controller according to  $1/\sqrt{m}$ , thus influencing the transformation between the bipolar and the unipolar signal. When the parameter m and c vary, system (2) has the same Lyapunov exponents as indicated by the shifted and rescaled equilibrium points of saddle-foci  $(-c,0,\pm 1/\sqrt{m})$  with fixed eigenvalues  $(-0.7709,0.3855\pm 1.5639i)$  as shown in Fig. 6. For a=1, and m=4, the amplitude of the variables x and z are scaled by 1/2 while the amplitude of variable y remains the same as shown in Fig. 7. When the offset-boosting controller c varies, the attractor shifts along the x axis.

**Fig. 6.** (color online) Regulated amplitudes and offsets and the Lyapunov exponents of system (2) with initial condition (1, 1, -1): (a) amplitude rescaling with constant Lyapunov exponents (b) offset boosting with constant Lyapunov exponents.

Fig. 7. (color online) Strange attractor of system (2) with a = 1, m = 4 in (a) x-y plane and (b) x-z plane.

## 3. Linear synchronization

In addition to the complete amplitude control of the chaotic signal in a single chaotic system as mentioned above, it may also be necessary to obtain a similar linear control in a synchronization system<sup>[29,32–36]</sup> where the chaotic signal of the driven system is the linear transformation of the one from the driving system. This is defined as "linear generalized synchronization" or "linear synchronization". <sup>[37,38]</sup> In the following, we construct a synchronization system of this type.

**Theorem 1** Suppose that a chaotic driving system x is described by,

$$\dot{\boldsymbol{x}} = \boldsymbol{A}\boldsymbol{x} + \boldsymbol{f}(\boldsymbol{x}),\tag{3}$$

where  $\boldsymbol{x} \in \boldsymbol{R^n}$  is the state vector of the system, while  $\boldsymbol{A} \in \boldsymbol{R^{n \times n}}$  is a constant matrix,  $\boldsymbol{f} : \boldsymbol{R^n} \to \boldsymbol{R^n}$  is Lipschitz continuous, that is, there exist positive constants l such that  $|f(w) - f(v)| \le l||w - v||$ ,  $w, v \in \boldsymbol{R^n}$ . The driven system  $\boldsymbol{y}$  can obtain a linear general synchronization [29,30] with the driving system,

$$\dot{\mathbf{y}} = KAK^{-1}(\mathbf{y} - \mathbf{B}) + Kf(K^{-1}(\mathbf{y} - \mathbf{B})) + \mathbf{u}, \quad (4)$$

where  $K = \text{diag}(k_1k_2,...,k_n)$ ,  $B = (b_1b_2,...,b_n)$ , and the controller is  $u = -\eta e$ , here  $\dot{\eta} = \theta e^T e$ ,  $(\theta > 0)$ , the error vector is defined as e = y - (Kx + B).

**Proof** From the error vector and systems (3) and (4), it yields

$$\dot{e} = \dot{y} - K\dot{x} = KAK^{-1}e$$

0.5

$$+K\left(f\left(K^{-1}\left(y-B

ight)

ight)-f\left(x

ight)

ight)-\eta e.$$

Choose

$$oldsymbol{V} = rac{1}{2}oldsymbol{e}^{\mathrm{T}}oldsymbol{e} + rac{1}{2oldsymbol{ heta}}(oldsymbol{\eta} \!-\! oldsymbol{\eta}^*)^2,$$

then

$$egin{aligned} \dot{V} &= e^{ ext{T}} \dot{e} + (\eta - \eta^*) \dot{\eta} / heta = e^{ ext{T}} K A K^{-1} e \ &+ e^{ ext{T}} K \left( f \left( K^{-1} \left( y - B

ight)

ight) - f \left( x

ight)

ight) - \eta^* e^{ ext{T}} e \ &\leq ||KAK^{-1}|| e^{ ext{T}} e + l e^{ ext{T}} e - \eta^* e^{ ext{T}} e \ &= \left( ||KAK^{-1}|| + l - \eta^*

ight) e^{ ext{T}} e = -e^{ ext{T}} e, \end{aligned}$$

where  $\|\cdot\|$  denotes the  $l_2$ -norm. Therefore, the driving system and the driven system can finally go to synchronization. Here  $\eta^* = ||KAK^{-1}|| + l + 1$ . Here the elements in matrix K and matrix B represent the slope and intercept of the linear function, which is determined by the relation between two groups of synchronized variables. Theoretically, the control parameters  $k_i$  and  $b_i$  can be set arbitrarily. The synchronization performance is related with the coefficient  $\theta$  positively.

Specifically, for system (2), the driving system can be written as

$$\begin{cases} \dot{x}_1 = ax_2x_3, \\ \dot{x}_2 = 1 - mx_3^2, \\ \dot{x}_3 = x_1 + x_2x_3 + c. \end{cases}$$

(5)

**Fig. 8.** (color online) Synchronization curves: (a) error between  $y_i$  and  $kx_i + b$ , (b) relationship between  $x_i$  and  $y_i$ , attractors in driving system and driven system in panels (c) and (d).

We construct the driven system as

$$\begin{cases} \dot{y}_1 = k_1 a (y_2 - b_2) (y_3 - b_3) k_2^{-1} k_3^{-1} - \eta e_1, \\ \dot{y}_2 = k_2 - k_2 m (y_3 - b_3)^2 k_3^{-2} - \eta e_2, \\ \dot{y}_3 = k_3 k_1^{-1} (y_1 - b_1) + k_2^{-1} (y_2 - b_2) (y_3 - b_3) + k_3 c - \eta e_3. \end{cases}$$

(6)

Here  $e_1 = y_1 - (k_1x_1 + b_1)$ ,  $e_2 = y_2 - (k_2x_2 + b_2)$ ,  $e_3 = y_3 - (k_3x_3 + b_3)$ ,  $\dot{\eta} = e_1^2 + e_2^2 + e_3^2$ . Select a = m = c = 1,  $k_1 = -1$ ,  $k_2 = 2$ ,  $k_3 = 0.5$ ,  $b_1 = b_2 = b_3 = 1$ , choose the initial conditions of the driving system  $(x_{10}, x_{20}, x_{30})$  and driven system  $(y_{10}, y_{20}, y_{30})$  as (0.1, 0.1, 0.1) and (-0.1, 0.2, -0.1),  $\eta_0 = 0$ , two systems can obtain a linear synchronization as shown in Fig. 8.

# 4. FPAA-based Circuit implementation

FPGA-based circuit implementation has the advantages in both hardware and software, which is reliable, flexible and has the advantage of fast response, rapid prototyping, adaptation, reduced cost or simplicity of design for the programmable architecture. [39,40] Field programmable analog arrays (FPAA) also provide such a workbench for circuit realization, in particular it is more convenient to design the analog chaotic circuits. Therefore recently FPAA has become more and more popular, and it has been used in many areas, such as system modeling, signal processing, fault-tolerant, and computing feature extraction. Comparing with the technology of Field–Programmable Gate Array (FPGA), it is not nec-

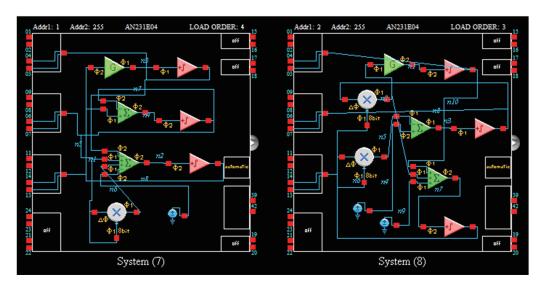

essary to make a discretization with the variables in FPAA. Here in this paper we use the newest integrated circuit technique of FPAA to realize the system discussed above. An Anadigm QuadApex development board with four AN231E04 chips [41–44] was used to construct a circuit implementation of systems (1) and (2) and to experimentally verify the amplitude control and offset boosting. Each chip contains four Configurable Analog Blocks (CABs) which perform the analog processing through using the fully differentiable switched capacitor technology. Because the dpASP has a differential output voltage level of  $\pm 3$  V, amplitude rescaling is necessary. First, System (1) was rescaled to  $x \rightarrow 12x$ ,  $y \rightarrow 8y$ ,  $z \rightarrow 8z$  as follows:

$$\begin{cases} \dot{x} = 0.667az, \\ \dot{y} = -by + z, \\ \dot{z} = -1.5x + y + 8my^2 + 0.125c. \end{cases}$$

(7)

Then system (2) was rescaled to  $x \to 4x$ ,  $y \to 4y$ ,  $z \to 4z$  as follows:

$$\begin{cases} \dot{x} = 4ayz, \\ \dot{y} = 0.25 - 4mz^2, \\ \dot{z} = x + 4yz + 0.25c. \end{cases}$$

(8)

The circuits were then constructed using Configurable Analog Modules (CAMs) in AnadigmDesigner2 as shown in Fig. 9 and downloaded to the development board. CAM values for systems (7) and (8) are given in Tables 1 and 2.

$\textbf{Fig. 9.} \ (\text{color online}) \ Circuit \ implementations \ of \ system \ (7) \ and \ system \ (8) \ on \ Anadigm Designer 2.$

The phase portraits for systems (7) and (8) are shown in Figs. 10 and 12, respectively. To observe offset boosting and amplitude control in system (7), we changed Inputs 3 and 4 in SumDiff2. Offset boosting in system (8) can be observed by changing Input 3 in SumDiff2. The signals were collected using an NI USB 6002 at a sample rate of 5 kHz after time scaling, and are shown in Fig. 11 for system (7) and in Fig. 13 for system (8), respectively. Note that the linear synchronization can also be proved by FPAA since the driving system and the driven system can be regarded as a higher-dimensional analog system. Here in this paper, we emphasize the convenience of amplitude control and offset control obtained from this new technology.

**Table. 1.** CAM parameters for system (7) circuit.

# Configurable Analog Modules: System (7)

| Name                               | Options                  |                | Parameters                   |         | Clocks |                                         |

|------------------------------------|--------------------------|----------------|------------------------------|---------|--------|-----------------------------------------|

| Integrator1                        | Polarity                 | Non-inverting  | Integration Const.           | 0.00250 | ClockA | 250 kHz (Chip Clock                     |

| (Integrator v1.1.1)                | Input Sampling           | Phase 1        | [1/us]                       | 0.00250 | CIOCKE | 3)                                      |

|                                    | Phase<br>Compare Control |                |                              |         |        |                                         |

| <b>■</b>                           | То                       | No Reset       |                              |         |        |                                         |

| Anadigm                            |                          |                |                              |         |        |                                         |

| (Approved)                         |                          |                |                              |         |        |                                         |

| Integrator2<br>(Integrator v1.1.1) | Polarity                 | Non-inverting  | Integration Const.<br>[1/us] | 0.00250 | ClockA | 250 kHz (Chip Clock<br>3)               |

| (                                  | Input Sampling<br>Phase  | Phase 2        | [1/45]                       |         |        | 3)                                      |

| Φ2                                 | Compare Control<br>To    | No Reset       |                              |         |        |                                         |

| Anadigm                            |                          |                |                              |         |        |                                         |

| (Approved) Integrator3             | <b>D.</b> 1.             |                |                              |         |        | *************************************** |

| (Integrator v1.1.1)                | Polarity Input Sampling  | Non-inverting  | Integration Const.<br>[1/us] | 0.00250 | ClockA | 250 kHz (Chip Clock<br>3)               |

|                                    | Phase                    | Phase 2        | []                           |         |        | -/                                      |

| ■ <del> </del>                     | Compare Control<br>To    | No Reset       |                              |         |        |                                         |

| Anadigm<br>(Approved)              |                          |                |                              |         |        |                                         |

| SumDiff2                           | Output Phase             | Phase 2        | Gain 1 (UpperInput)          | 1.50    | ClockA | 250 kHz (Chip Clock                     |

| (SumDiff v1.0.1)                   | Input 1                  | Inverting      | Gain 2 (SecondInput)         | 1.00    |        | 3)                                      |

| Φ1 Φ2                              | Input 2                  | Non-inverting  | Gain 3 (ThirdInput)          | 16.0    |        |                                         |

| Φ1<br>Φ2                           | Input 3                  | Non-inverting  | Gain 4 (LowerInput)          | 0.333   |        |                                         |

| Anadigm                            | Input 4                  | Inverting      |                              |         |        |                                         |

| (Approved) GainHalf1               | D. 1                     | N              |                              |         |        | 250 LTL (Cl.:. Cl L                     |

| (GainHalf v1.0.1)                  | Polarity                 | Non-inverting  | Gain                         | 1.33    | ClockA | 250 kHz (Chip Clock<br>3)               |

| ■ <sub>Φ2</sub> G <sup>Φ1</sup> ■  | Input Sampling<br>Phase  | Phase 2        |                              |         |        | <i>y</i> ,                              |

| Anadigm                            |                          |                |                              |         |        |                                         |

| (Approved)                         |                          |                |                              |         |        |                                         |

| Multiplier1<br>(Multiplier v1.0.2) | Sample and Hold          | Off            | Multiplication Factor        | 1.00    | ClockA | 250 kHz (Chip Clock<br>3)               |

| <b>Φ</b> 1 <b>Φ</b> 1              |                          |                |                              |         | ClockB | 4 MHz (Chip Clock 0)                    |

| 4nadiam                            |                          |                |                              |         |        |                                         |

| Anadigm<br>(Approved)              |                          |                |                              |         |        |                                         |

| SumDiff1                           | Output Phase             | Phase 2        | Gain 1 (UpperInput)          | 2.00    | ClockA | 250 kHz (Chip Clock                     |

| (SumDiff v1.0.1)                   | Input 1                  | Inverting      | Gain 2 (LowerInput)          | 1.00    | CIOCKA | 3)                                      |

| Φ2                                 | Input 2                  | Non-inverting  |                              |         |        |                                         |

| Ф1                                 | Input 3                  | Off            |                              |         |        |                                         |

| Anadigm<br>(Approved)              | Input 4                  | Off            |                              |         |        |                                         |

| Voltage1                           | Polarity                 | Positive (+2V) |                              |         |        |                                         |

| (Voltage v1.0.1)                   |                          |                |                              |         |        |                                         |

| <b>*</b>                           |                          |                |                              |         |        |                                         |

| Anadigm                            |                          |                |                              |         |        |                                         |

| (Approved)                         |                          |                |                              |         |        |                                         |

**Table. 2.** CAM parameters for system (8) circuit.

# Configurable Analog Modules: System (8)

| Name                               | Options                 |                      | Parameters            |         | Clocks   |                           |

|------------------------------------|-------------------------|----------------------|-----------------------|---------|----------|---------------------------|

| Integrator1                        | Polarity                | Non-inverting        | Integration Const.    | 0.00250 | ClockA   | 250 kHz (Chip Clock       |

| (Integrator v1.1.1)                | Input Sampling<br>Phase | Phase 2              | [1/us]                | 0.00230 | Clock4   | 3)                        |

| <b>■ 4 1 1</b>                     | Compare Control<br>To   | No Reset             |                       |         |          |                           |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| Multiplier1<br>(Multiplier v1.0.2) | Sample and Hold         | Off                  | Multiplication Factor | 1.00    | ClockA   | 250 kHz (Chip Clock<br>3) |

| Φ1 8bit Anadigm                    |                         |                      |                       |         | ClockB   | 4 MHz (Chip Clock 0)      |

| (Approved)                         |                         |                      |                       |         |          |                           |

| SumDiff1                           | Output Phase            | Phase 1              | Gain 1 (UpperInput)   | 4.00    | ClockA   | 250 kHz (Chip Clock       |

| (SumDiff v1.0.1)                   | Input 1                 | Inverting            | Gain 2 (LowerInput)   | 0.125   |          | 3)                        |

| <b>№</b> Ф1                        | Input 2                 | Non-inverting        |                       |         |          |                           |

| Ф2                                 | Input 3                 | Off                  |                       |         |          |                           |

| Anadigm<br>(Approved)              | Input 4                 | Off                  |                       |         |          |                           |

| Integrator3                        | Polarity                | Non-inverting        | Integration Const.    | 0.00250 | ClockA   | 250 kHz (Chip Clock       |

| (Integrator v1.1.1)                | Input Sampling<br>Phase | Phase 2              | [1/us]                | 0.00250 | ClockA   | 3)                        |

| Φ2                                 | Compare Control<br>To   | No Reset             |                       |         |          |                           |

| Anadigm                            |                         |                      |                       |         |          |                           |

| (Approved) Multiplier2             | Sample and Hold         | Off                  | Multiplication Factor | 1.00    | Classica | 250 kHz (Chip Clock       |

| (Multiplier v1.0.2)                | _                       |                      |                       |         | ClockA   | 3)                        |

| Φ1 Sbit                            |                         |                      |                       |         | ClockB   | 4 MHz (Chip Clock 0)      |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| Integrator2<br>(Integrator v1.1.1) | Polarity                | Non-inverting        | Integration Const.    | 0.00250 | ClockA   | 250 kHz (Chip Clock       |

| (antigration variate)              | Input Sampling<br>Phase | Phase 1              | [1/us]                |         |          | 3)                        |

| Φ1                                 | Compare Control<br>To   | No Reset             |                       |         |          |                           |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| SumDiff2                           | Output Phase            |                      | Gain 1 (UpperInput)   |         | ClockA   | 250 kHz (Chip Clock       |

| (SumDiff v1.0.1)                   | _                       | Non-inverting        | Gain 2 (MiddleInput)  |         |          | 3)                        |

| Φ1 Φ2                              |                         | Non-inverting        | Gain 3 (LowerInput)   | 0.750   |          |                           |

| Ф1                                 | Input 3<br>Input 4      | Non-inverting<br>Off |                       |         |          |                           |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| GainHalf1                          | Polarity                | Non-inverting        | Cein                  | 4.00    |          | 250 kHz (Chip Clock       |

| (GainHalf v1.0.1)                  | Input Sampling Phase    | Phase 1              | Gain                  |         | ClockA   | 3)                        |

| Φ1 G *2                            | 1 mase                  |                      |                       |         |          |                           |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| Voltage1<br>(Voltage v1.0.1)       | Polarity                | Positive (+2V)       |                       |         |          |                           |

| •                                  |                         |                      |                       |         |          |                           |

| Anadigm<br>(Approved)              |                         |                      |                       |         |          |                           |

| Voltage2                           | Polarity                | Positive (+2V)       |                       |         |          |                           |

| (Voltage v1.0.1)                   |                         |                      |                       |         |          |                           |

| ₹<br>Anadigm<br>(Approved)         |                         |                      |                       |         |          |                           |

| approved)                          |                         |                      |                       |         |          |                           |

Fig. 10. (color online) Phase portraits of system (3): (a) x-y plane, (b) x-z plane, and (c) y-z plane.

Fig. 11. (color online) Chaotic attractors of system (7) from circuit with different amplitudes rescaling and offset control in x-y and x-z planes.

Fig. 12. (color online) Phase portrait of system (4) in (a) x-y plane, (b) x-z plane, and (c) y-z plane.

Fig. 13. (color online) Chaotic attractors of system (8) from circuit with different amplitude rescaling and offset controls.

#### 5. Discussion and conclusions

We proposed a simple method for complete amplitude control in a single chaotic system and established a linear synchronization between two chaotic systems. Amplitude control is associated with amplification, attenuation and polarity inversion, which is important for signal conditioning and integrated circuit selection in electronic engineering. To realize a simple, convenient and reliable amplitude control of chaotic signals, two coefficients in the dynamical equations are found to have the function of rescaling and offset boosting. Those two independent coefficients correspond to two separate rheostats (or CAM gain values) which eliminate the need of a more complicated circuit and enhance the flexibility of the constructed circuit for chaos application. The proposed approach to the complete amplitude control for chaotic signals is of great value in chaos-based engineering applications.

#### References

- [1] Pecora L M and Carroll T L 1990 Phys. Rev. Lett. 64 821

- [2] Pecora L M and Carroll T L 1991 Phys. Rev. A 44 2374

- [3] Carroll T L and Pecora L M 1991 IEEE Trans. Circ. Syst. 38 453

- [4] Cuomo K M, Oppenheim A V and Strogatz S H 1993 IEEE Trans. Circ. Syst. II: Analog and Digital Signal Processing 40 626

- [5] Leung H and Lo T 1993 IEEE J. Oceanic. Eng. 18 287

- [6] Yang T 1995 Int. J. Circ. Theor. Appl. 23 611

- [7] Zhou C and Lai C H 1999 Phys. Rev. E 60 320

- [8] Corron N J and Hahs D W 1997 IEEE Trans. Circ. Syst. I: Fund. Th. Appl. 44 373

- [9] Lin F Y and Liu J M 2004 IEEE J. Quantum Elect. 40 815

- [10] Shi Z G, Qiao S, Chen K S, Cui W Z, Ma W, Jiang T and Ran L X 2007 Prog. Electromagn. Res. 77 1

- [11] Liu Z, Zhu X H, Hu W and Jiang F 2007 Int. J. Bifur. Chaos 17 1735

- [12] Murali K and Lakshmanan M 1998 Phys. Lett. A 241 303

- [13] Yupapin P P and Suwancharoen W 2007 Opt. Commun. 280 343

- [14] Wang A, Wang Y, and He H 2008 *IEEE Photon. Tech. Lett.* **20** 1633

- [15] Yu S and Chen G 2010 IEEE Trans. Circ. Syst. II: Express Briefs 57 803

- [16] Yu S, Chen G and Yu G 2011 IEEE Trans. Circ. Syst. II: Express Briefs 58 314

- [17] Yu S, Yu X and Chen G 2012 IEEE Trans. Circ. Syst. 1: Fund. Th. Appl. 59 1015

- [18] Sun K, He S, He Y and Yin L 2013 Acta Phys. Sin. 62 010501 (in Chinese)

- [19] Sun K, Wang X and Sprott J C 2010 Int .J. Bifur. Chaos 20 1209

- [20] Xu B and Wang G 2017 Acta Phys. Sin. 66 020502 (in Chinese)

- [21] Li C and Sprott J C 2013 Nonlinear Dyn. 73 1335

- [22] Li C, Sprott J C, Thio W and Zhu H 2014 IEEE Trans. Circ. Syst. II: Express Briefs 61 977

- [23] Li C, Sprott J C and Thio W 2015 Phys. Lett. A 379 888

- [24] Li C, Sprott J C, Yuan Z and Li H 2015 Int. J. Bifur. Chaos 25 1530025

- [25] Akutagawa T, Koshinaka H, Sato D, Takeda S, Noro S I, Takahashi H, Kumai R, Tokura, Y and Nakamura T 2009 Nat. Mater. 8 342

- [26] Lee D, Baek S H, Kim T H, Yoon J G, Folkman C M, Eom C B and Noh T W 2011 Phys. Rev. B 84 125305

- [27] Marchi M D,Sacchetto D, Frache S, Zhang J, Gaillardon P E, Leblebici Y and Micheli G D 2012 IEEE International, Electron Devices Meeting (IEDM) San Francisco, CA pp. 841–844

- [28] Li C, Pehlivan I and Sprott J C 2016 Turk. J. Elec. Eng. & Sci. 24 1

- [29] Li C and Sprott J C 2016 Optik 127 10389

- [30] Sprott J C 1994 Phys. Rev. E 50 647

- [31] Sprott J C 1997 Am. J. Phys. 65 537

- [32] Zhang R X, Yang S P and Liu Y L 2010 Acta Phys. Sin. 59 1549 (in Chinese)

- [33] Liu H, Li S G, Wang H X and Li G J 2017 Chin. Phys. B 26 030504

- [34] Tong P and Chen S H 2017 Chin. Phys. B 26 050503

- [35] Zhang X J, Wei A J and Li K Z 2016 Chin. Phys. B 25 038901

- [36] Ouannas A and Grassi G 2016 Chin. Phys. B 25 090503

- [37] Hu A and Xu Z 2008 Phys .Lett. A 372 3814

- [38] Wang Z, Sun W, Wei Z and Xi X 2014 Kybernetika 50 616

- [39] Cavuslu M A, Karakuzu C and Karakaya F 2012 Appl. Soft Comput. 12 2707

- [40] Tuntas R 2015 Appl. Soft Comput. 12 237

- [41] D'mello D R and Gulak P G 1998 Analog. Integr. Circ. S. 177

- [42] Caponetto R, Mauro A D, Fortuna L and Frasca M 2005 Int. J. Bifur. Chaos 15 1829

- [43] Kilic R and Dalkiran F Y 2009 Int. J. Bifur. Chaos 19 1339

- [44] Kilic R and Dalkiran F Y 2010 Turk. J. Elec. Eng. & Comp. Sci. 18 647